- 您现在的位置:买卖IC网 > Sheet目录2007 > LTC6994CDCB-2#TRPBF (Linear Technology)IC DELAY LINE 6-DFN

LTC6994-1/LTC6994-2

18

699412fb

applicaTions inForMaTion

Settling Time

Following a 2

× or 0.5× step change in ISET, the out-

put delay takes approximately six master clock cycles

(6 tMASTER) to settle to within 1% of the final value.

An example is shown in Figure 12, using the circuit in

Figure 10.

Figure 12. Typical Settling Time

VCTRL

2V/DIV

IN

5V/DIV

OUT

5V/DIV

DELAY

2s/DIV

LTC6994-1

V+ = 3.3V

DIVCODE = 0

RSET = 200k

RMOD = 464k

tOUT = 3s AND 6s

20s/DIV

699412 F12

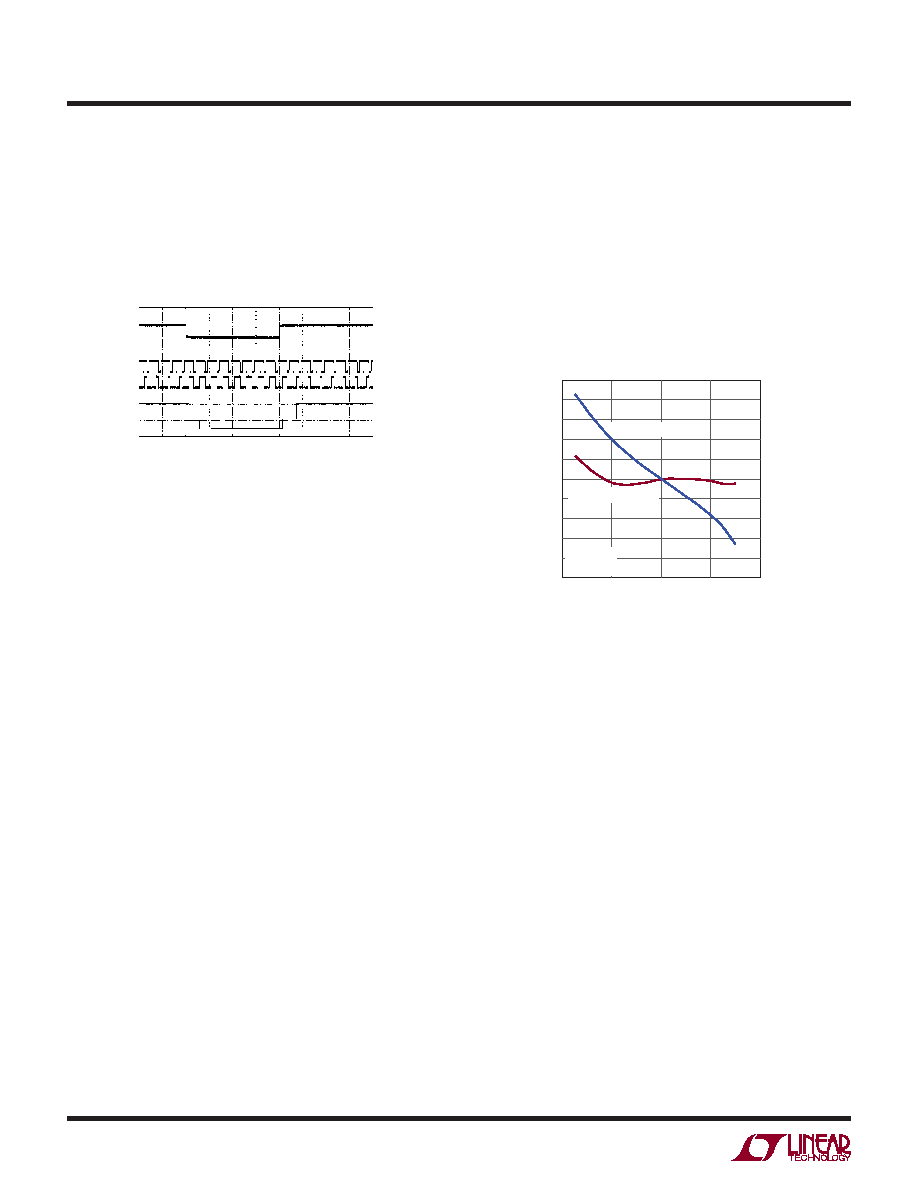

Coupling Error

The current sourced by the SET pin is used to bias the

internal master oscillator. The LTC6994 responds to

changesinISETalmostimmediately,whichprovidesexcel-

lent settling time. However, this fast response also makes

the SET pin sensitive to coupling from digital signals, such

as the IN input.

Even an excellent layout will allow some coupling between

IN and SET. Additional error is included in the specified

accuracy for NDIV = 1 to account for this. Figure 13 shows

that ÷1 supply variation is dependent on coupling from

rising or falling inputs.

A very poor layout can actually degrade performance

further. The PCB layout should avoid routing SET next to

IN (or any other fast-edge, wide-swing signal).

SUPPLY (V)

2

–1.0

0

0.4

0.2

0.6

0.8

1.0

4

5

6

–0.4

–0.2

–0.6

–0.8

3

699412 F13

DRIFT

(%)

FALLING EDGE DELAY

RISING EDGE DELAY

RSET = 50k

NDIV = 1

Figure 13. Delay Drift vs Supply Voltage

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LTC7541ABN#PBF

IC CMOS D/A CONV 12BIT 18-DIP

LTC7545ACG#TRPBF

IC D/ACONV MULTIPLY 12BIT 20SSOP

LTC8043EN8

IC D/A CONV 12BIT SERIAL 8-DIP

LTC8143ESW#TRPBF

IC D/A CONV 12BIT SERIAL 16-SOIC

LTM9011CY-14#PBF

IC ADC 14BIT UMODULE 140BGA

LV5609LP-E

IC CLOCK DRIVER VERTICAL 24VCT

LV5609LP-TE-L-E

IC CLOCK DRIVER VERT VCT24

M-986-2A1PL

IC TRANSCEIVER MF 2CHAN 44-PLCC

相关代理商/技术参数

LTC6994CDCB-2TRMPBF

制造商:LINER 制造商全称:Linear Technology 功能描述:TimerBlox: Delay Block/ Debouncer

LTC6994CS6-1#PBF

制造商:Linear Technology 功能描述:SC-Timing, Cut Tape Delay with Rising or Falling Edge Trigger

LTC6994CS6-1#TRMPBF

功能描述:IC DELAY LINE TSOT-23-6 RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:TimerBlox® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR)

LTC6994CS6-1#TRPBF

功能描述:IC DELAY LINE TSOT-23-6 RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:TimerBlox® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR)

LTC6994CS6-1TRMPBF

制造商:Linear Technology 功能描述:Delay Block/Debouncer 1us-33.6s TSOT23-6

LTC6994CS6-2#PBF

制造商:Linear Technology 功能描述:DELAY BLOCK/DEBOUNCER 5.5V T 制造商:Linear Technology 功能描述:DELAY BLOCK/DEBOUNCER, 5.5V, TSOT-23-6; Operating Mode:Monostable; Supply Voltage Min:2.25V; Supply Voltage Max:5.5V; Digital IC Case Style:TSOT-23; No. of Pins:6; Clock External Input:Yes; Operating Temperature Min:0C ;RoHS Compliant: Yes

LTC6994CS6-2#TRMPBF

功能描述:IC DELAY LINE TSOT-23-6 RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:TimerBlox® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR)

LTC6994CS6-2#TRPBF

功能描述:IC DELAY LINE TSOT-23-6 RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 延迟线 系列:TimerBlox® 标准包装:2,500 系列:- 标片/步级数:- 功能:多个,不可编程 延迟到第一抽头:10ns 接头增量:- 可用的总延迟:10ns 独立延迟数:4 电源电压:4.75 V ~ 5.25 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SOIC 包装:带卷 (TR)